注文金額が

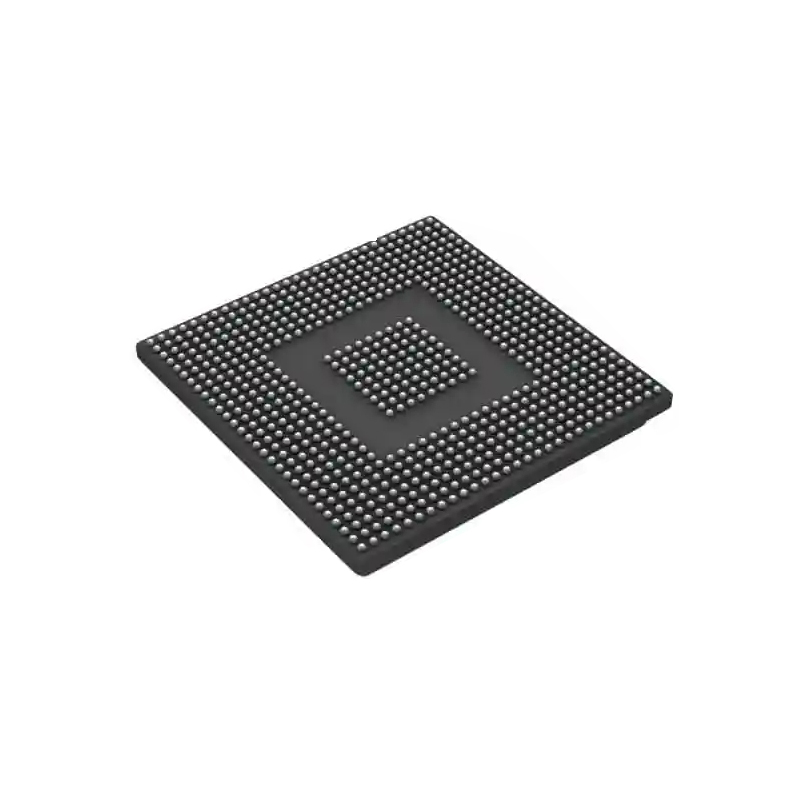

$5000Intel EP2S60F672C5

Advanced Stratix II FPGA for high-performance applications

EP2S60F672C5 概要

Built for high-performance applications, the EP2S60F672C5 FPGA is a versatile device that offers superior processing power and connectivity options. With 60,000 logic elements and 672 I/O pins, this FPGA is capable of handling complex algorithms and data-intensive tasks with ease. Its 1.5 Mb embedded memory enables efficient implementation of advanced signal processing and video processing applications, making it an ideal choice for demanding projects. The EP2S60F672C5 also supports various communication protocols like PCI Express and Gigabit Ethernet, providing flexible connectivity options for networking applications. Additionally, its clocking resources, including PLLs and DLLs, ensure precise timing control for reliable performance

特徴

- The Stratix II family offers the following

- features:

- 15,600 to 179,400 equivalent LEs; see Table 1–1

- New and innovative adaptive logic module (ALM), the basic building block of the Stratix II architecture, maximizes performance and resource usage efficiency

- Up to 9,383,040 RAM bits (1,172,880 bytes) available without reducing logic resources

- TriMatrix memory consisting of three RAM block sizes to implement true dual-port memory and first-in first-out (FIFO) buffers

- High-speed DSP blocks provide dedicated implementation of multipliers (at up to 450 MHz), multiply-accumulate functions, and finite impulse response (FIR) filters

- Up to 16 global clocks with 24 clocking resources per device region

- Clock control blocks support dynamic clock network enable/disable, which allows clock networks to power down to reduce power consumption in user mode

- Up to 12 PLLs (four enhanced PLLs and eight fast PLLs) per device provide spread spectrum, programmable bandwidth, clock switchover, real-time PLL reconfiguration, and advanced multiplication and phase shifting

- Support for numerous single-ended and differential I/O standards

- High-speed differential I/O support with DPA circuitry for 1-Gbps performance

- Support for high-speed networking and communications bus standards including Parallel RapidIO, SPI-4 Phase 2 (POS-PHY Level 4), HyperTransport™ technology, and SFI-4

- Support for high-speed external memory, including DDR and DDR2 SDRAM, RLDRAM II, QDR II SRAM, and SDR SDRAM

- Support for multiple intellectual property megafunctions from Altera MegaCore® functions and Altera Megafunction Partners Program (AMPPSM) megafunctions

- Support for design security using configuration bitstream encryption

- Support for remote configuration updates

仕様

| パラメータ | 価値 | パラメータ | 価値 |

|---|---|---|---|

| Rohs Code | No | Part Life Cycle Code | Obsolete |

| Ihs Manufacturer | INTEL CORP | Package Description | 35 X 35 MM, 1 MM PITCH, FBGA-672 |

| Reach Compliance Code | compliant | HTS Code | 8542.39.00.01 |

| Samacsys Manufacturer | Intel | Clock Frequency-Max | 640 MHz |

| Combinatorial Delay of a CLB-Max | 5.962 ns | JESD-30 Code | S-PBGA-B672 |

| JESD-609 Code | e0 | Length | 35 mm |

| Moisture Sensitivity Level | 3 | Number of CLBs | 24176 |

| Number of Inputs | 492 | Number of Logic Cells | 60440 |

| Number of Outputs | 484 | Number of Terminals | 672 |

| Operating Temperature-Max | 85 °C | Operating Temperature-Min | |

| Organization | 24176 CLBS | Package Body Material | PLASTIC/EPOXY |

| Package Code | BGA | Package Equivalence Code | BGA672,26X26,40 |

| Package Shape | SQUARE | Package Style | GRID ARRAY |

| Power Supplies | 1.2,1.5/3.3,3.3 V | Programmable Logic Type | FIELD PROGRAMMABLE GATE ARRAY |

| Qualification Status | Not Qualified | Seated Height-Max | 2.6 mm |

| Supply Voltage-Max | 1.25 V | Supply Voltage-Min | 1.15 V |

| Supply Voltage-Nom | 1.2 V | Surface Mount | YES |

| Technology | CMOS | Temperature Grade | OTHER |

| Terminal Finish | TIN LEAD | Terminal Form | BALL |

| Terminal Pitch | 1.27 mm | Terminal Position | BOTTOM |

| Width | 35 mm |

配送

| 配送タイプ | 配送料 | リードタイム | |

|---|---|---|---|

|

DHL | $20.00-$40.00 (0.50 KG) | 2-5 日々 |

|

フェデックス | $20.00-$40.00 (0.50 KG) | 2-5 日々 |

|

UPS | $20.00-$40.00 (0.50 KG) | 2-5 日々 |

|

TNT | $20.00-$40.00 (0.50 KG) | 2-5 日々 |

|

EMS | $20.00-$40.00 (0.50 KG) | 2-5 日々 |

|

登録された航空便 | $20.00-$40.00 (0.50 KG) | 2-5 日々 |

処理時間:送料は地域や国によって異なります。

支払い

| 支払条件 | ハンドフィー | |

|---|---|---|

|

電信送金 | 銀行手数料 US$30.00 を請求します。 |

|

ペイパル | 4.0%のサービス料がかかります。 |

|

クレジットカード | 3.5%のサービス料がかかります。 |

|

ウエスタンユニオン | charge US.00 banking fee. |

|

送金サービス | 銀行手数料は 0.00 米ドルかかります。 |

保証

1.購入した電子部品には365日保証が含まれており、製品の品質を保証します。

2.受け取った商品の一部が完璧な品質ではない場合、当社は責任を持って返金または交換を手配します。 ただし、商品は元の状態のままでなければなりません。

パッキング

-

![製品 製品]()

ステップ1 :製品

-

![真空包装 真空包装]()

ステップ2 :真空包装

-

![静電気防止袋 静電気防止袋]()

ステップ3 :静電気防止袋

-

![個包装 個包装]()

ステップ4 :個包装

-

![梱包箱 梱包箱]()

ステップ5 :梱包箱

-

![バーコード配送タグ バーコード配送タグ]()

ステップ6 :バーコード配送タグ

すべての製品は静電気防止袋に梱包されます。 ESD 帯電防止保護を備えた状態で出荷されます。

社外の ESD 梱包ラベルには、部品番号、ブランド、数量などの当社の情報が使用されます。

私たちは出荷前にすべての商品を検査し、すべての製品が良好な状態であることを確認し、部品が新しいオリジナルでデータシートと一致していることを確認します。

すべての商品に問題がないことを確認した後、梱包後、安全に梱包し、グローバルエクスプレスで発送します。 優れた耐穿刺性と耐引裂性を示し、シールの完全性も良好です。

私たちは高品質の製品、思いやりのあるサービス、販売後の保証を提供します

-

![製品 製品]()

豊富な商品を取り揃えておりますので、お客様の様々なニーズにお応え致します。

-

![quantity quantity]()

最小注文数量は1個からとなります。

-

![shipping shipping]()

最低国際配送料は0.00ドルから

-

![保証 保証]()

全商品365日品質保証